ขนาดของเวเฟอร์ซิลิโคนไม่ใช่สิ่งที่คุณคิดและชิปขนาดเล็กอย่างไม่น่าเชื่อเหล่านี้ “3nm” และ “2nm” ที่คุณยังได้ยินอยู่? พวกเขามีการตลาดมากกว่าการวัด

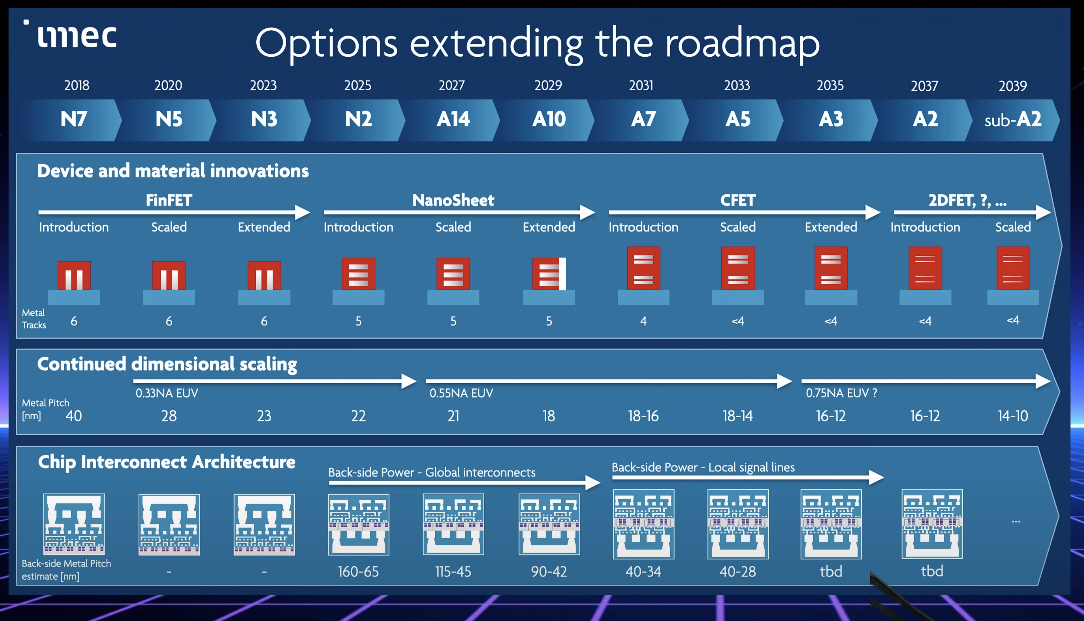

การคาดการณ์ล่าสุดของศูนย์ไมโครอิเล็กทรอนิกส์อินเตอร์ -อูนีเรีย (IMEC) ซึ่งเพิ่งหารด้วย YouTuber TechTechpotato นำเสนอตารางเวลาปัจจุบันของชิปกระบวนการ TSMC 2NM และ A10 (1NM) ในปี 2029 IMEC Evool ความเป็นไปได้ในการผลิตซิลิกอน 0.2 มม. เร็วเท่าปี 2039

ในความเป็นจริงตัวเลขเหล่านี้แตกต่างจากทรานซิสเตอร์ทางกายภาพที่วัดได้บนชิปและบางทีเราอาจต้องรอจนถึงสิ้นยุค 1830 ยุค 1830 ก่อนที่เราจะจัดการทำลายสิ่งกีดขวาง 10 นาโนเมตร นี่คือเหตุผล

เวเฟอร์ซิลิโคนไม่เล็กเท่ากับขนาดที่สองมันจะทำให้คุณคิด

ปัจจุบัน 2-nanometers และ 1.8 nm Silicon Technologies ตาม TSMC และ Intel ไม่ได้ผลิตขึ้นสำหรับเวเฟอร์ที่หนา 2nm

2nm ยังไม่ได้ระยะห่างระหว่างสองทรานซิสเตอร์บนวาฟเฟิล

ผู้ผลิตชิปเกี่ยวข้องกับเวเฟอร์ซิลิคอนตามขนาดขั้นต่ำของคุณสมบัติที่ได้รับบนพื้นผิวของกระเบื้องระหว่างการผลิต ในขณะนี้ขนาดนี้มักหมายถึง ชื่อ โหนดขั้นตอนแทนลักษณะทางกายภาพใด ๆ ของระบบ

ในความเป็นจริงชื่อของการทดลองซิลิคอนไม่ถูกต้องตั้งแต่ปี 1997 โหนดกระบวนการ Intela 250 nm จริงมีความยาวประตู 200 นาโนเมตร Intel ยังคงดำเนินต่อไปจากการพิจารณาคดีจนถึงปี 2011 เมื่อการทดลองของซิลิคอนลดลงเหลือ 22 นาโนเมตรโดยมีความยาวเป้าหมายที่แท้จริง 26 นาโนเมตร

TSMC และ Samsung ยังยอมรับ “การตลาดการรับรู้” สำหรับซิลิคอนในปี 2561 ด้วยโหนดกระบวนการ 7NM ซึ่งคล้ายกันในแง่ของความยาวของเป้าหมายสูงถึง 10 นาโนเมตรของ Intel Silicon

และความสับสนยังคงหมุนอยู่

อย่างไรก็ตามหากคุณกำลังมองหาการวัดทางกายภาพที่ยากสำหรับชิป 3 นาโนเมตรปัจจุบันพวกเขามีความยาวเป้าหมาย 16-18 นาโนเมตรและจังหวะโลหะประมาณ 23 นาโนเมตร

ดังนั้นโดยไม่คำนึงถึงการสนทนาในปัจจุบันของครั้งที่สองและ 3nm เราอาจจะไม่เห็นซิลิกอน 10 นาโนเมตร “ของจริง” ตราบใดที่ IMEC ทำนายการสร้างชิปเซ็ตย่อย A2 ในปี 2039

ขนาดและกฎหมายของมัวร์

ในฐานะที่เป็นเครื่องดื่มอย่างรวดเร็วกฎหมายของมัวร์เป็นการสังเกตโครงการไมโครชิปโดยระบุว่าจำนวนทรานซิสเตอร์ในวงจรบูรณาการเพิ่มขึ้นเป็นสองเท่าในทุก ๆ สองปี เมื่อเวเฟอร์ซิลิคอนมีขนาดเล็กลงเช่นเดียวกับทรานซิสเตอร์ แต่ในที่สุดทุกสิ่งต้องโค้งคำนับตามกฎของฟิสิกส์

ตรงกันข้ามกับชื่อกฎหมายของมัวร์ไม่ใช่กฎหมายที่แท้จริง แต่เป็นการสังเกตการออกแบบไมโครชิป ในที่สุดเซมิคอนดักเตอร์อาจมีขนาดเล็กก่อนที่ความร้อนของวงจรจะกลายเป็นปัญหาการออกแบบที่แท้จริง

ซีอีโอของ Nvidia, Jensen Huang, ตรงกันข้ามกับความคิดที่จะดำเนินการต่อแนวโน้มในด้านกฎหมายของมัวร์ส่วนใหญ่เป็นผลมาจากข้อ จำกัด ทางความร้อนที่สูงขึ้นเกี่ยวกับการ์ดกราฟิกที่ไม่ต่อเนื่องในขณะที่โปรเซสเซอร์เช่นชิปเซ็ต Intel Lake Lake

แต่ด้วยการเตือนความจำของ IMEC เกี่ยวกับกระเบื้องซิลิคอนขนาดจริงและการปรับปรุงที่คาดหวังในสถาปัตยกรรมสถาปัตยกรรมและเทคโนโลยีทรานซิสเตอร์กฎหมายของมัวร์ดูเหมือนไม่จริง ไม่ว่าแนวโน้มจะคงอยู่ในทศวรรษหน้าเราไม่สามารถพูดได้อย่างแน่นอน แต่ดูเหมือนว่าจะประสบความสำเร็จขึ้นอยู่กับการคาดการณ์ปัจจุบัน

ที่จะบอกว่าจำนวนทรานซิสเตอร์ที่มีศักยภาพในชิปเซ็ตย่อย A2 (10 นาโนเมตร) นั้นน่าทึ่ง ปัจจุบัน Intel Core Ultra 9 285K มีทรานซิสเตอร์ประมาณ 18 พันล้านตัวซึ่งหมายความว่าชิปเซ็ตย่อย A2 สามารถมีทรานซิสเตอร์ประมาณ 300 พันล้านทรานซิสเตอร์ในปี 2039